Questo articolo illustra la sostituzione degli switch PhotoMOS con degli switch CMOS nei sistemi di collaudo automatico (ATE).

Questo articolo illustra la sostituzione degli switch PhotoMOS con degli switch CMOS nei sistemi di collaudo automatico (ATE).

Gli switch CMOS non solo offrono i vantaggi prestazionali dei PhotoMOS in termini di prodotto capacità-resistenza (CxR), ma offrono anche velocità di accensione (turn-on), affidabilità e scalabilità superiori, che li rendono adatti a soddisfare le esigenze in continua evoluzione dei sistemi ATE nell'era dei test sulle memorie avanzate.

La crescente domanda di memorie ad alte prestazioni, in particolare di memorie ad ampia larghezza di banda (HBM, High Bandwidth Memory), nelle applicazioni di intelligenza artificiale (AI) sta portando allo sviluppo di progetti di chip sempre più complessi

I produttori di sistemi di collaudo automatico, che sono strumenti fondamentali per la verifica di questi componenti, stanno affrontando una pressione crescente per tenere il passo con questa domanda. Tradizionalmente, nelle applicazioni di alimentazione delle sonde per il test su wafer dei chip di memoria, gli interruttori PhotoMOS trovano impiego grazie alle loro caratteristiche di bassa capacità per resistenza.

Un basso prodotto CxR aiuta a ridurrre la distorsione del segnale, migliorando l’isolamento in condizione off e offrendo velocità di commutazione elevate e bassa perdita di inserzione.

Nonostante questi vantaggi e l'elevata tensione di stand-off, gli switch PhotoMOS presentano alcuni limiti. Questi includono l'affidabilità, la scalabilità e la velocità di accessione. La lentezza nell'accensione è sempre stata un punto di insoddisfazione per i clienti.

Per affrontare queste sfide, Analog Devices (ADI) ha sviluppato degli switch che sostituiscono i PhotoMOS nelle applicazioni di alimentazione delle sonde per il test su wafer delle memorie. Gli switch di ADI offrono velocità di accensione elevate e possiedono lo stesso basso valore del prodotto CxR, garantendo una commutazione efficiente.

Inoltre, la scalabilità di questi switch migliora il parallelismo dei test, consentendo agli utilizzatori degli ATE di gestire processi di test più estesi e più rapidi. Queste caratteristiche rendono gli switch ADI una valida alternativa ai PhotoMOS, soprattutto quando i produttori di ATE faticano di soddisfare la crescente domanda di test di memoria efficienti e ad alte prestazioni nelle applicazioni emergenti dell'AI.

In un tester ATE, gli switch svolgono un ruolo cruciale nel facilitare il processo di test, consentendo la connessione e la disconnessione di più dispositivi in prova (DUT, Device Under Test) a un singolo strumento di misura, come un'unità di misura parametrica (PMU, Parametric Measurement Unit).

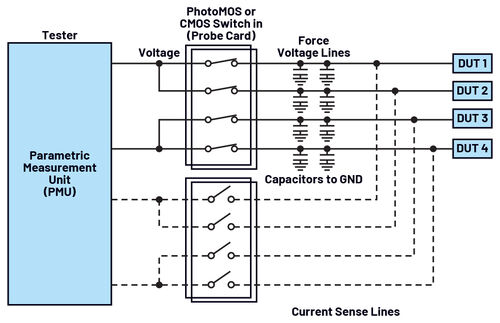

Fig. 1 - Commutazione dei segnali in un tester ATE per collegare le unità di misura (PMU) ai dispositivi in prova (DUT)

Fig. 1 - Commutazione dei segnali in un tester ATE per collegare le unità di misura (PMU) ai dispositivi in prova (DUT)

Come descritto, gli switch permettono alle PMU di erogare tensioni specifiche verso vari DUT e di rilevare in modo efficiente il feedback di corrente da questi stessi DUT. Gli switch semplificano il processo di test, in particolare negli scenari in cui più DUT devono essere valutati in parallelo o in sequenza. La capacità di indirizzare la tensione dalla PMU a più DUT, insieme al rilevamento delle correnti da quest’ultimi, ottimizza la produttività del test e riduce al minimo la necessità di riconfigurare gli strumenti di test tra una prova e l'altra.

La Figura 1 mostra come gli switch possano facilitare la creazione di una configurazione a matrice, consentendo a una PMU di valutare più DUT. Questa configurazione migliora la flessibilità e la scalabilità dei sistemi ATE, riducendo la necessità di utilizzare PMU multiple e la complessità del cablaggio, che è fondamentale per le configurazioni di test ad alto volume o multidispositivo.

Per comprendere li risultato del confronto tra uno switch PhotoMOS e uno switch CMOS utilizzando le schede di valutazione hardware sviluppate a tale scopo, Il punto di partenza migliore è rappresentato dalle architetture degli switch di entrambi.

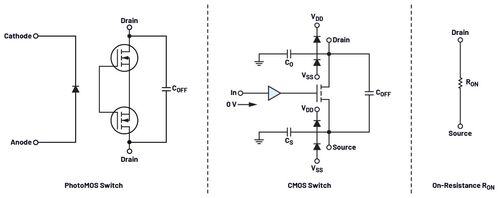

Fig. 2 - Architetture degli switch PhotoMOS e CMOS

Fig. 2 - Architetture degli switch PhotoMOS e CMOS

Mentre le architetture di un interruttore CMOS e di un interruttore PhotoMOS sembrano essere diverse, la Figura 2 mostra la capacità in condizione off (COFF), ossia quando gli switch sono spenti. Questa capacità parassita si trova tra il pin source di ingresso e il pin di uscita.

Per uno switch PhotoMOS, la COFF si trova tra i pin drain di uscita. Inoltre, lo switch PhotoMOS presenta una capacità tra ingresso e uscita (o capacità di drain) e una capacità di ingresso sullo stadio del diodo a emissione luminosa (LED) utilizzato per l'accensione e lo spegnimento dei MOSFET di uscita.

Per uno switch CMOS, la COFF si trova tra i pin source e drain. Oltre alla COFF, per uno switch CMOS sono presenti la capacità di drain (CD) e la capacità di source (CS) verso massa. Anche queste capacità verso massa sono un motivo di insoddisfazione dei clienti che utilizzano switch CMOS.

Quando uno switch è abilitato a far passare i segnali di ingresso verso l'uscita, la resistenza di conduzione (RON) è tra i pin di source e drain. Comprendendo questi dettagli dell'architettura, diventa più facile analizzare parametri di prestazione come la capacità, la RON e il comportamento di commutazione negli studi di valutazione, assicurando la scelta del tipo di switch corretto per applicazioni specifiche.

Un modo migliore per qualificare e quantificare gli switch consiste nell'esaminare il contributo del valore aggiunto in un'applicazione di progettazione a livello di sistema. Come accennato, per l'applicazione di Figura 1, lo switch ADG1412 risulta particolarmente adatto e può essere facilmente utilizzato al posto di uno switch PhotoMOS.

Questo switch CMOS è un comutataro in configurazione quadruplo SPST (Single-Pole, Single-Throw) con caratteristiche eccellenti in termini di gestione della potenza, tempo di risposta, resistenza di conduzione e correnti residue.

Confrontando le prestazioni dello switch CMOS con i parametri più importanti, come illustrato nella Tabella 1, la scheda di valutazione permette ai progettisti di quantificare i suoi meriti rispetto alle alternative. Ciò potrebbe fornire maggiori informazioni sull'efficienza del dispositivo nella commutazione dei segnali, soprattutto in sistemi elettronici complessi o sensibili.

|

Criteri di Benchmark |

PhotoMOS |

ADG1412 |

Valore Aggiunto |

Punteggio |

|---|---|---|---|---|

|

Leakage |

1 nA |

30 pA |

Ideale per i test di perdita; minore contributo all'errore di tensione in uscita |

Migliore per switch CMOS |

|

COFF |

0,45 pF |

1,6 pF |

Minore distorsione della forma d'onda, maggiore isolamento |

Migliore per PhotoMOS |

|

RON |

12 Ω |

1,5 Ω |

Basse cadute di tensione del segnale |

Migliore per CMOS switch |

|

Prodotto (CxR) |

5,4 pF x Ω |

2,4 pF x Ω* |

Minore distorsione della forma d'onda, maggiore isolamento e bassa perdita |

Appena superiore per PhotoMOS switch grazie alla bassa capacità di drain |

|

Capacità di Drain [CD(OFF)] |

1 pF |

23 pF |

Un valore più alto degrada |

Migliore per PhotoMOS |

|

Velocità di Turn-on |

200 μs |

100 ns |

Velocità di switch più elevata |

Migliore per CMOS switch |

|

Specifiche di tensione e corrente |

(32 V, 120 mA) |

(32 V, 250 mA) |

Capacità di passare una corrente |

Migliore per CMOS switch |

|

Costo/canale |

Alto |

Basso |

Favorisce l'aumento della densità |

Migliore per CMOS switch |

|

Ingombro del package |

3,55 mm2 |

4,00 mm2 per switch |

Le superfici degli switch equivalgono |

Quasi identico per entrambi |

* CD(OFF) influenza le prestazioni del prodotto CxR

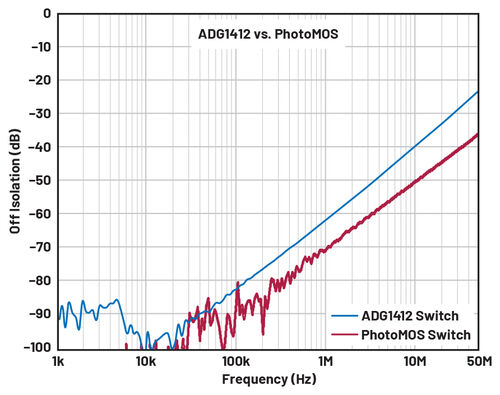

I grafici dell'isolamento in condizione off (Figura 3) per entrambi gli switch indicano un'elevata soppressione (-80 dB a 100 kHz) dei segnali di ingresso che non raggiungono l'uscita.

Caratteristica di isolamento quando lo switch è aperto (off)

Caratteristica di isolamento quando lo switch è aperto (off)

Il PhotoMOS si comporta marginalmente meglio, con -10 dB all'aumentare della frequenza. Per l'applicazione di commutazione mostrata nella Figura 1, che indica la commutazione in corrente continua (DC), le capacità dello switch non sono importanti; piuttosto, i parametri di riferimento dello switch sono la corrente residua (leakage) ridotta, l’alta velocità di accensione e la perdita di inserzione.

Uno switch con una RON bassa è fondamentale. La caduta di tensione I*R limita le prestazioni del sistema. Una bassa variazione di RON da un componente all'altro e in base alla temperatura riduce l'errore di misura.

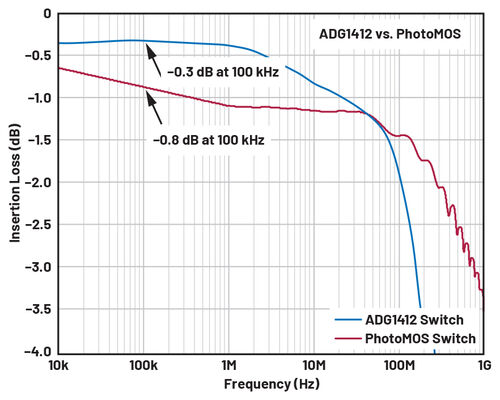

Fig. 4 - Perdita di inserzione quando lo switch è chiuso

Fig. 4 - Perdita di inserzione quando lo switch è chiuso

Il grafico della perdita di inserzione nella Figura 4 mostra che lo switch PhotoMOS ha una riduzione di -0,8 dB a 100 kHz rispetto allo switch CMOS (-0,3 dB) alla stessa frequenza.

Ciò rafforza il basso valore di RON (1,5 Ω) dello switch CMOS.

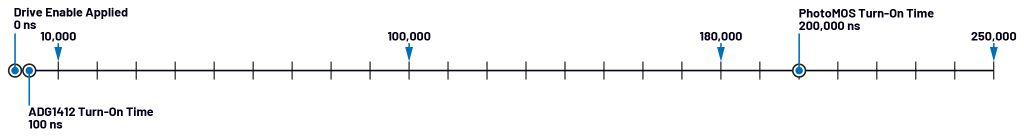

Dal momento in cui una tensione sull'ingresso enable/logic applicata a uno dei due switch ne provoca la chiusura e il passaggio dei segnali di ingresso all'uscita, nel caso di utilizzo di uno switch PhotoMOS si prevede un tempo di ritardo significativo (Figura 5).

Fig. 5 - Tempo di commutazione dello switch

Fig. 5 - Tempo di commutazione dello switch

Questa bassa velocità di chiusura è dovuta alla capacità dello stadio di ingresso del LED e al ritardo dovuto alla circuiteria interna utilizzata per la conversione corrente/tensione necessaria per pilotare i gate dei MOSFET.

Queste basse velocità di chiusura hanno sempre rappresentato un notevole motivo di insoddisfazione per i clienti, rallentando e condizionando l'applicazione complessiva del sistema. Lo switch CMOS ha una velocità di chiusura elevata (100 ns), ideale per le applicazioni di sistema, rispetto allo switch PhotoMOS (200.000 ns). Un valore duemila (2000) volte più basso!

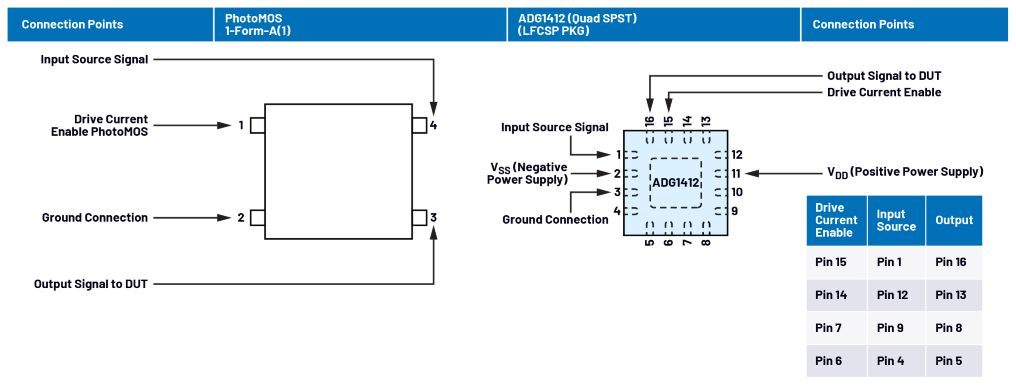

Per i sistemi che utilizzano switch PhotoMOS, dove esistono problemi in termini di imprecisioni di misura, rallentamenti del sistema a causa della lentezza delle velocità di commutazione e dell'incapacità di ottenere un'adeguata densità dei canali, l'aggiornamento del progetto intoducendo uno switch CMOS è incredibilmente facile.

Fig. 6 - Progetto di migrazione da uno switch PhotoMOS allo switch CMOS ADG1412

Fig. 6 - Progetto di migrazione da uno switch PhotoMOS allo switch CMOS ADG1412

La Figura 6 mostra i punti di connessione di uno switch PhotoMOS mappati su quelli dello switch CMOS. Pertanto, i progetti di sistema possono utilizzare gli switch disponibili per aumentare la densità dei canali a un costo ridotto.

Figura 6. Punti di connessione degli switch

La Tabella 2 elenca alcuni esempi di switch ADI che permettono di aumentare la densità dei canale in un sistema di collaudo automatico.

Questi switch offrono vantaggi in termini di prestazioni come quelli dell'ADG1412, hanno una resistenza di conduzione molto più bassa di almeno 0,5 Ω e hanno un costo ridotto rispetto agli switch PhotoMOS.

Questi switch sono disponibili sia con interfaccia seriale SPI (Serial Peripheral Interface) che con interfaccia parallela, per consentire connessioni semplici ai processori di controllo.

|

Prodotto |

RON (Ω) |

Configurazione Switch |

Prezzo di Listino/Ch ($) 1ku |

|---|---|---|---|

|

0,5 |

Quad-SPST |

Molto Competitivo |

|

|

0,5 |

Quad-SPST |

Molto Competitivo |

|

|

0,56 |

SPI: Octal-SPST |

Molto Competitivo |

Questa analisi evidenzia il potenziale di utilizzo di uno switch CMOS.

Il dispositivo integrato ADG1412 costituisce una valida alternativa agli switch PhotoMOS nelle applicazioni ATE.

Il confronto dei benchmark mostra che lo switch CMOS soddisfa o supera le aspettative di prestazioni, soprattutto in scenari in cui la capacità dello switch o la capacità di drain non sono critiche.

Inoltre, lo switch CMOS offre notevoli vantaggi, tra cui una maggiore densità dei canali e l'economicità.

Il portafoglio di switch CMOS di ADI, che comprende varianti con una minore resistenza di conduzione e interfacce di controllo sia parallele che SPI, rafforza ulteriormente la possibilità di adottarli nei sistemi ATE.

*Edwin Omoruyi è Senior Applications Engineer in Analog Devices