Misure su bus seriali veloci e DDR

- Dettagli

- Scritto da Simone Castelli

- Categoria: Oscilloscopi

Tektronix ha presentato un nuovo pacchetto software per i suoi oscilloscopi delle serie DPO/DSA/MSO70000 dedicato all'analisi dei bus seriali veloci e deli segnali delle memorie DDR.

Tektronix ha presentato un nuovo pacchetto software per i suoi oscilloscopi delle serie DPO/DSA/MSO70000 dedicato all'analisi dei bus seriali veloci e deli segnali delle memorie DDR.

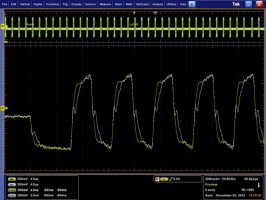

Il nuovo pacchetto applicativo Serial Data Link Analysis Visualizer (SDLA Visualizer) permette di modellare le caratteristiche di un collegamento dati veloce per estrarre qualsiasi componente di segnale dal percorso di misura, per simulare delle componenti virtuali di un collegamento, per applicare diversi parametri di equalizzazione e per eseguire misure in più punti della catena di trattamento del segnale appartenente a un sistema, un modulo o un chip.

SDLA Visualizer di caratterizzazione il livello fisico del bus seriali veloci e dei bus di memoria ad alta velocità mettendo in relazione tra di loro, con un buon livello di confidenza, il comportamento teorico del segnale calcolato da un modello matematico, con il segnale fisico reale misurato.

Per comprendere a fondo il comportamento dei segnali più veloci in sistemi che adottano le più sofisticate tecniche di equalizzazione, il software SDLA Visualizer mette a disposizione un modello completo a 4 porte che permette di tener conto dell'impedenza di uscita del trasmettitore, l'impedenza di ingresso dell'oscilloscopio e quella del ricevitore, nonchè l'impedenza della connessione e del dispositivo di collaudo (fixture) per fornire la rappresentazione del segnale più fedele possible.

Per comprendere a fondo il comportamento dei segnali più veloci in sistemi che adottano le più sofisticate tecniche di equalizzazione, il software SDLA Visualizer mette a disposizione un modello completo a 4 porte che permette di tener conto dell'impedenza di uscita del trasmettitore, l'impedenza di ingresso dell'oscilloscopio e quella del ricevitore, nonchè l'impedenza della connessione e del dispositivo di collaudo (fixture) per fornire la rappresentazione del segnale più fedele possible.

Per ottenere una corretta rappresentazione del segnale reale si tiene conto e si possono compensare artificialmente gli effetti dovuti alle riflessioni del segnale, alle perdite di inserzione e ai dei termini del mutuo accoppiamento tra ogni elemento che entra a far parte della linea di collegamento in esame. Inoltre, è possible verificare il comportamento del collegamento e di ogni suo elemento costitutivo in tremini di parametri S.

Per ottenere una corretta rappresentazione del segnale reale si tiene conto e si possono compensare artificialmente gli effetti dovuti alle riflessioni del segnale, alle perdite di inserzione e ai dei termini del mutuo accoppiamento tra ogni elemento che entra a far parte della linea di collegamento in esame. Inoltre, è possible verificare il comportamento del collegamento e di ogni suo elemento costitutivo in tremini di parametri S.

Il nuovo pacchetto software proposto da Tektronix permette anche di validare il modello della linea di trasmissione che costitusice la connessione sfruttando una serie completa di diagrammi che mostrano la risposta in frequenza, la risposta in fase, e l'andamento di tutti e sedici i parametri S previsti.

SDLA Visualizer usato assieme al pacchetto software DPOJET dedicato all'analisi del jitter tramite diagrammi a occhio consente di validare i risultati delle misure relative all'occhio e al jitter esamninandoli in vari punti della catena di trasferimento del segnale garantendo in tal modo che il modello utilizzato sia configurato correttamente.

Per facilitare il lavoro con i sistemi di equalizzazione integrati all'interno di chip in silicio, SDLA Visualizer non solo supporta tutte le principali tecniche di equalizzazione utilizzate dal ricevitore di riferimento, ma può anche utilizzare le particolare equalizzazioni e algoritmi per il recupero del clock specifici definiti da ciascun fornitore di circuiti integrati, aiutando in tal modo a configurare ed a definire il modello della connessione. Il software Tektronix supporta allo scompo i modelli basati sullo standard IBIS Algorithmic Modeling Interface (IBIS-AMI) per il livello fisico dei collegamenti seriali.